MULTIPLEXING INPUT/OUTPUT PROCESSOR MODELS 8271/8471 AND 8272/8472

SCIENTIFIC DATA SYSTEMS

### **TECHNICAL MANUAL**

# MULTIPLEXING INPUT/OUTPUT PROCESSOR

MODELS 8271/8471 AND 8272/8472

May 1968

# LIST OF EFFECTIVE PAGES

Total number of pages is 156, as follows:

| Page No.              | Issue    | Page No. | Issue |

|-----------------------|----------|----------|-------|

| Title                 | Original |          |       |

| Α                     | Original |          |       |

| i thru iv             | Original |          |       |

| 1-1 thru 1-2          | Original |          |       |

| 2-1 thru 2-2          | Original |          |       |

| 3-1 thru <b>3-142</b> | Original |          |       |

| 4-1 thru 4-4          | Original |          |       |

## CONTENTS

| I   GENERAL DESCRIPTION   1-1   1-1   1-1   Introduction   1-2   Physical Description   1-1   1-2   Physical Description   1-1   1-3   Functional Description   1-1   1-4   Specifications and Leading Particulars   1-1   1-4   Specifications and Leading Particulars   1-1   1-1   1-2   General   2-1   General   2-1   General   2-1   3-1   Introduction   3-1   3-1   Introduction   3-1   3-2   General Principles of Operation   3-1   3-3   General   3-3   Genera | Section |                                                                                                                                                                                                                                                                                                                     | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I       | GENERA                                                                                                                                                                                                                                                                                                              | L DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-1                                                                                                    |

| 2-1       General       2-1         III       PRINCIPLES OF OPERATION       3-1         3-1       Introduction       3-1         3-2       General Principles of Operation       3-1         3-3       General       3-1         3-4       Overall Operation       3-1         3-5       Interrupt Calls       3-3         3-6       Chaining       3-3         3-7       Detailed Principles of Operation       3-3         3-8       MIOP Register       3-3         3-9       A Register       3-3         3-10       C-Register       3-3         3-11       C-Register       3-7         3-12       BA-Register       3-7         3-13       BC-Register       3-7         3-14       FS-Register       3-7         3-15       OF-Register       3-8         3-16       IS-Register       3-10         3-17       F-Register       3-10         3-18       H-Register       3-10         3-19       J-Register       3-11         3-20       1-Register       3-11         3-21       O-Register       3-11         3-22 <t< td=""><td></td><td>1 <b>-</b>2<br/>1 <b>-</b>3</td><td>Physical Description</td><td>1 -1<br/>1 -1</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | 1 <b>-</b> 2<br>1 <b>-</b> 3                                                                                                                                                                                                                                                                                        | Physical Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 -1<br>1 -1                                                                                           |

| III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | II      | OPERATI                                                                                                                                                                                                                                                                                                             | ON AND PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-1                                                                                                    |

| 3-1       Introduction       3-1         3-2       General Principles of Operation       3-1         3-3       General       3-1         3-4       Overall Operation       3-1         3-5       Interrupt Calls       3-3         3-6       Chaining       3-3         3-7       Detailed Principles of Operation       3-3         3-8       MIOP Registers       3-3         3-9       A-Register       3-3         3-10       C-Register       3-3         3-11       CA-Register       3-3         3-12       BA-Register       3-7         3-13       BC-Register       3-7         3-14       FS-Register       3-7         3-15       OF-Register       3-7         3-15       OF-Register       3-8         3-16       IS-Register       3-10         3-17       F-Register       3-10         3-18       H-Register       3-10         3-19       J-Register       3-11         3-20       Islaster       3-11         3-21       O-Register       3-11         3-22       S-Register       3-11         3-23       M-Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         | 2-1                                                                                                                                                                                                                                                                                                                 | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-1                                                                                                    |

| 3-2       General Principles of Operation       3-1         3-3       General       3-1         3-4       Overall Operation       3-1         3-5       Interrupt Calls       3-3         3-6       Chaining       3-3         3-7       Detailed Principles of Operation       3-3         3-8       MIOP Registers       3-3         3-9       A-Register       3-3         3-10       C-Register       3-3         3-11       CA-Register       3-7         3-12       BA-Register       3-7         3-13       BC-Register       3-7         3-14       FS-Register       3-7         3-15       OF-Register       3-8         3-16       IS-Register       3-10         3-17       F-Register       3-10         3-18       H-Register       3-10         3-19       J-Register       3-11         3-20       I-Register       3-11         3-21       O-Register       3-11         3-22       S-Register       3-11         3-23       M-Register       3-14         3-24       W-Register       3-14         3-25       Ad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | III     | PRINCIP                                                                                                                                                                                                                                                                                                             | LES OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-1                                                                                                    |

| 3-36 TIO, TIO, and IDV instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16<br>3-17<br>3-18<br>3-19<br>3-20<br>3-21<br>3-22<br>3-23<br>3-24<br>3-25<br>3-24<br>3-25<br>3-27<br>3-28<br>3-27<br>3-28<br>3-29<br>3-30<br>3-31<br>3-32<br>3-33<br>3-34<br>3-35<br>3-35<br>3-36 | Introduction General Principles of Operation General Overall Operation Interrupt Calls Chaining Detailed Principles of Operation MIOP Registers A-Register C-Register C-Register BA-Register BA-Register BC-Register BC-Register FS-Register OF-Register IS-Register IS-Register I-Register M-Register M- | 3-1<br>3-1<br>3-1<br>3-3<br>3-3<br>3-3<br>3-3<br>3-7<br>3-7<br>3-7<br>3-7<br>3-7<br>3-1<br>3-11<br>3-1 |

# CONTENTS (Cont.)

| Section                                                                                                                                                          | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                  | 3-40 Order-Out Service Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-68<br>3-85<br>3-85<br>3-117<br>3-135                                                                                                                      |

| IV                                                                                                                                                               | MAINTENANCE AND PARTS LIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-1                                                                                                                                                         |

|                                                                                                                                                                  | 4-1       General         4-2       Preventive Maintenance         4-3       External Visual Inspection         4-4       Internal Visual Inspection         4-5       MIOP Test Programs         4-6       Parts List Table    TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-1<br>4-1<br>4-1<br>4-1<br>4-1                                                                                                                             |

| Table                                                                                                                                                            | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                                                                                                                                                        |

| 1-1<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16<br>3-17<br>3-18<br>3-19<br>4-1<br>4-2 | General Specifications.  MIOP/Memory Interface Signals.  MIOP/CPU Interface Signals.  Condition Code Settings.  MIOP/Device Controller Interface.  MIOP/Device Controller Interface.  MIOP/Device Controller Interface Line Utilization  Data Input/Output Line Definition  Data Order Request and Input/Output Request Line Definitions  Function Response Line Definition  Coding of End Data and End Service Lines During Data In/Out Operations.  Permitted Next States of End Data and End Service Lines  MIOP/Memory Phase Sequence  SIO Instruction Phase Sequence  HIO, TIO, and TDV Instruction Phase Sequence  AIO Instruction Phase Sequence  Order-Out Service Cycle Phase Sequence  Order-in Service Cycle Phase Sequence  Data-Out Service Cycle Phase Sequence  Data-In Service Cycle Phase Sequence  Glossary of MIOP Signals  Checkout Programs for MIOP  Multiplexing Input/Output Processor, Replaceable Parts | 1-I<br>3-22<br>3-24<br>3-25<br>3-27<br>3-28<br>3-29<br>3-30<br>3-30<br>3-44<br>3-47<br>3-56<br>3-63<br>3-72<br>3-89<br>3-97<br>3-121<br>3-135<br>4-1<br>4-2 |

| <b>-</b> •                                                                                                                                                       | ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                             |

| Figure 1-1 3-1 3-2 3-3 3-4 3-5 3-6 3-7 3-8 3-9                                                                                                                   | Title  MIOP Basic and Optional Subchannel Locations.  I/O System, Simplified Overall Block Diagram.  Loading Core Memory Location X'20' During an SIO Instruction  MIOP Block Diagram.  A-Register Inputs.  C-Register Inputs.  BA- and CA-Register Inputs.  BC- and FS-Register Inputs.  OF- and IS-Register Inputs.  F-Register Inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page 1-2 3-2 3-5 3-7 3-8 3-9 3-9 3-10 3-11                                                                                                                  |

SDS 901515 Illustrations

# ILLUSTRATIONS (Cont.)

| Figure        | Title                                                                                | Page          |

|---------------|--------------------------------------------------------------------------------------|---------------|

| 3-10          | H- and J-Register Inputs                                                             | 3-12          |

| 3-11          | I-Register Inputs                                                                    | 3-12          |

| 3-12          | O-Register Inputs                                                                    | 3-13          |

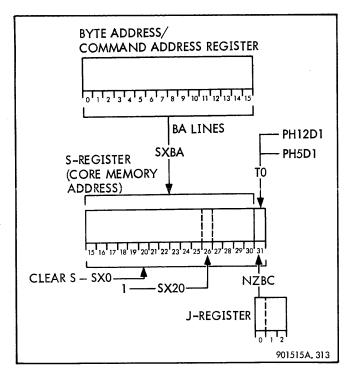

| 3-13          | S-Register Inputs                                                                    | 3-14          |

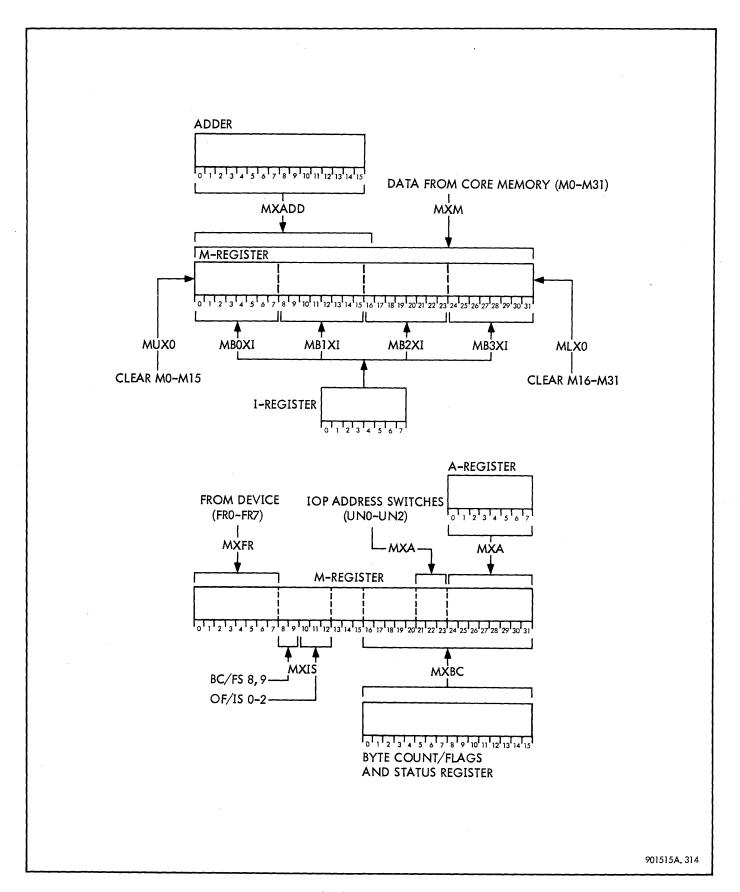

| 3-14          | M-Register Inputs                                                                    | 3-15          |

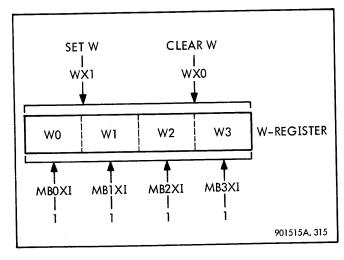

| 3-15          | W-Register Inputs                                                                    | 3-16          |

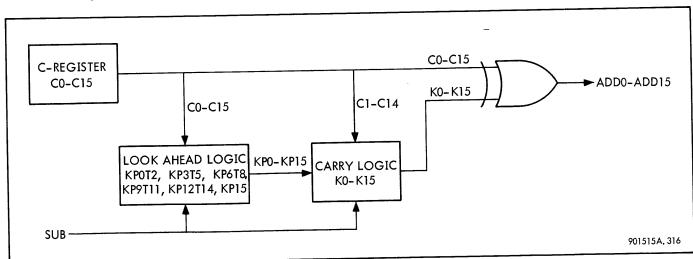

| 3-16          | Adder, Overall Block Diagram                                                         | 3-16          |

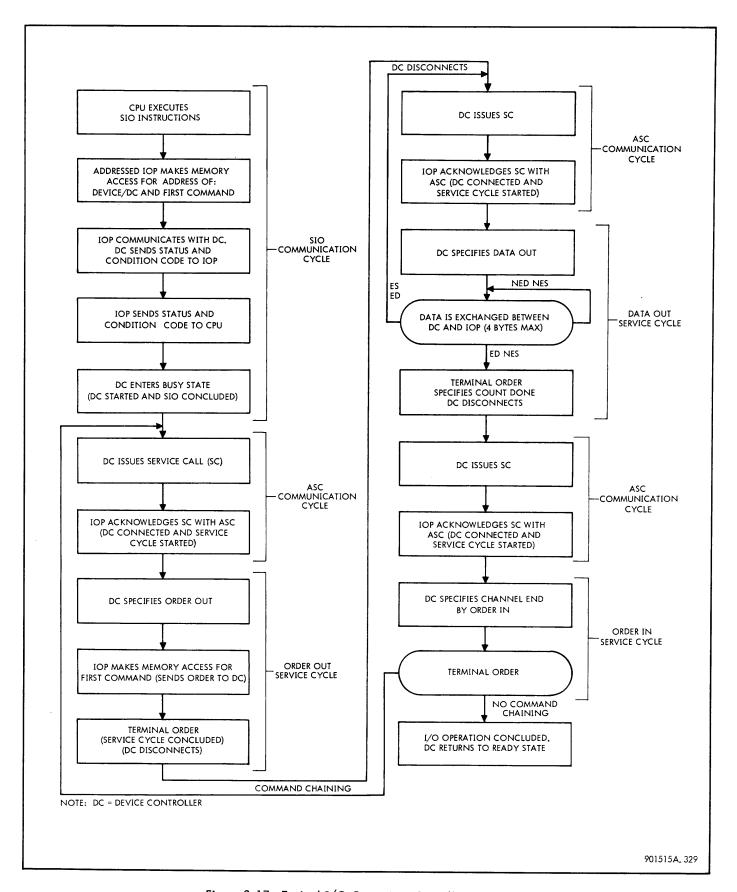

| 3-17          | Typical I/O Operation, Overall Sequence Diagram                                      | 3-17          |

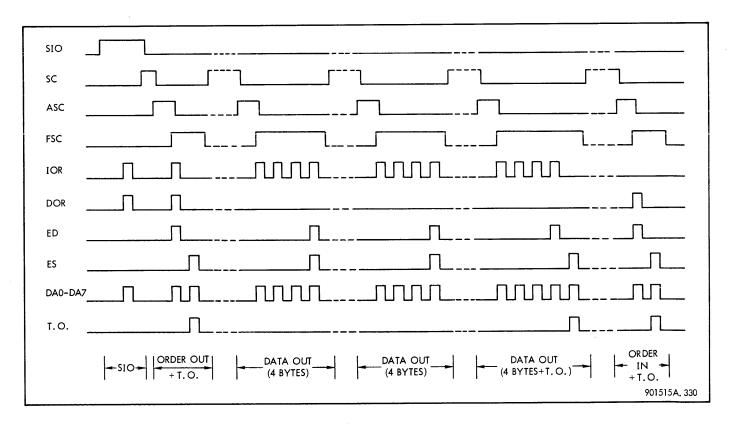

| 3-18          | Typical I/O Operation, Timing Diagram                                                | 3-18          |

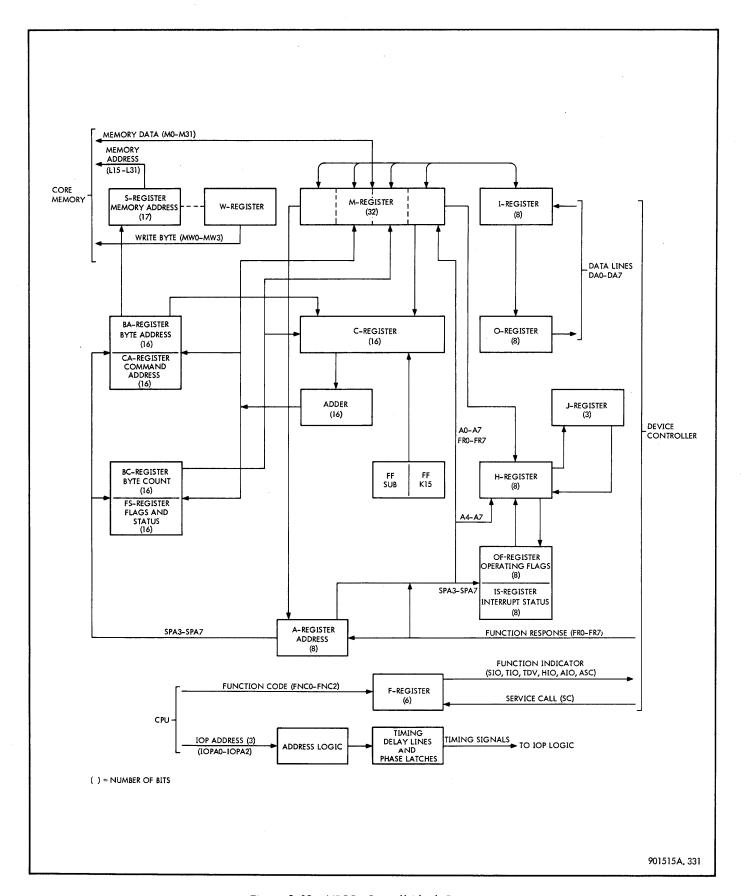

| 3-19          | MIOP, Overall Block Diagram                                                          | 3-19          |

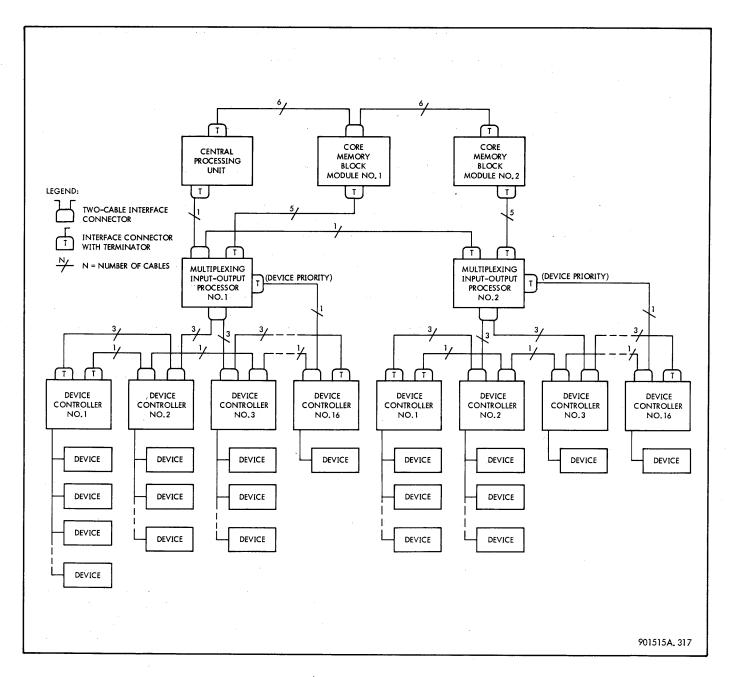

| 3-20          | I/O System Interconnection Diagram                                                   | 3-21          |

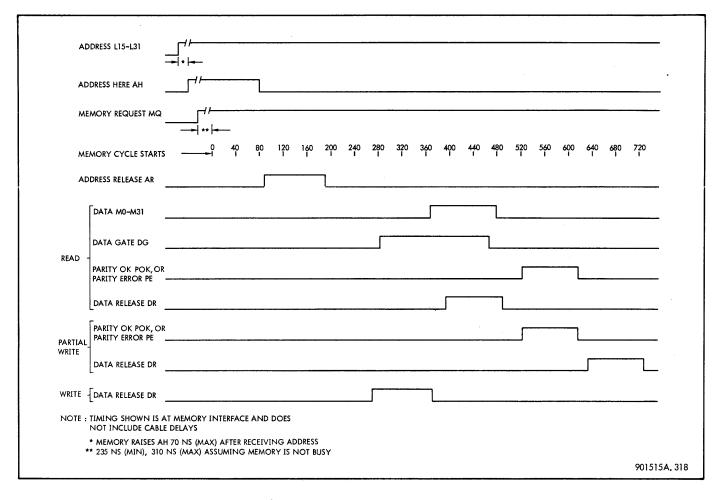

| 3-21          | MIOP/Memory Interface Signal Timing Diagram (Port A or B)                            | 3-22          |

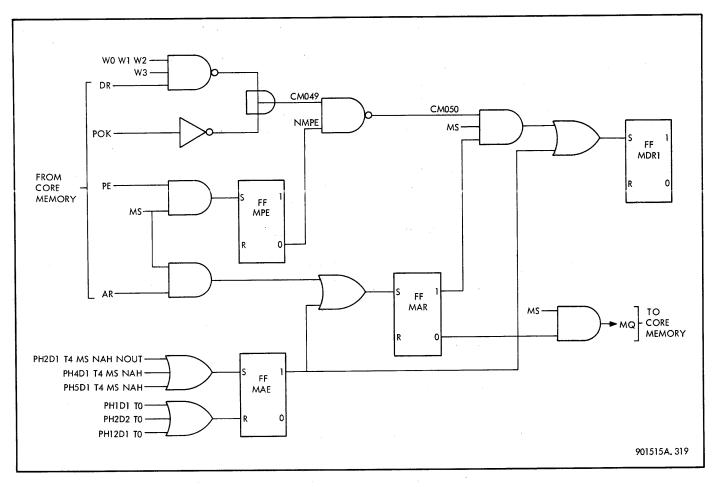

| 3-22          | Setting Memory Data Release Flip-Flop MDR1                                           | 3-24          |

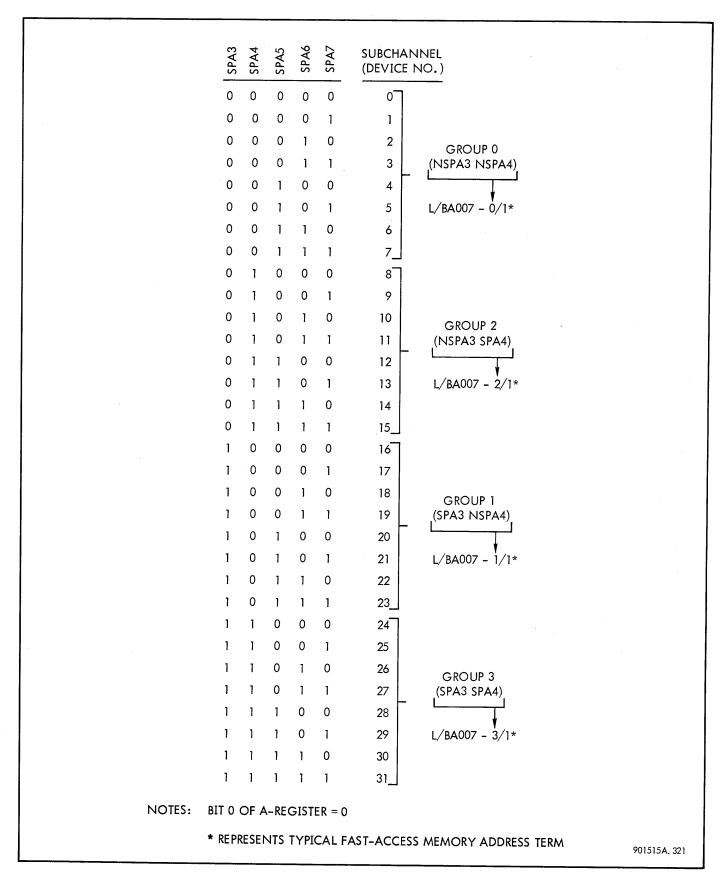

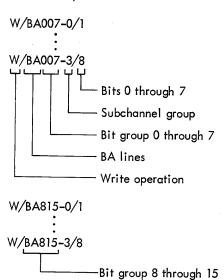

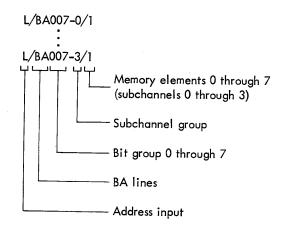

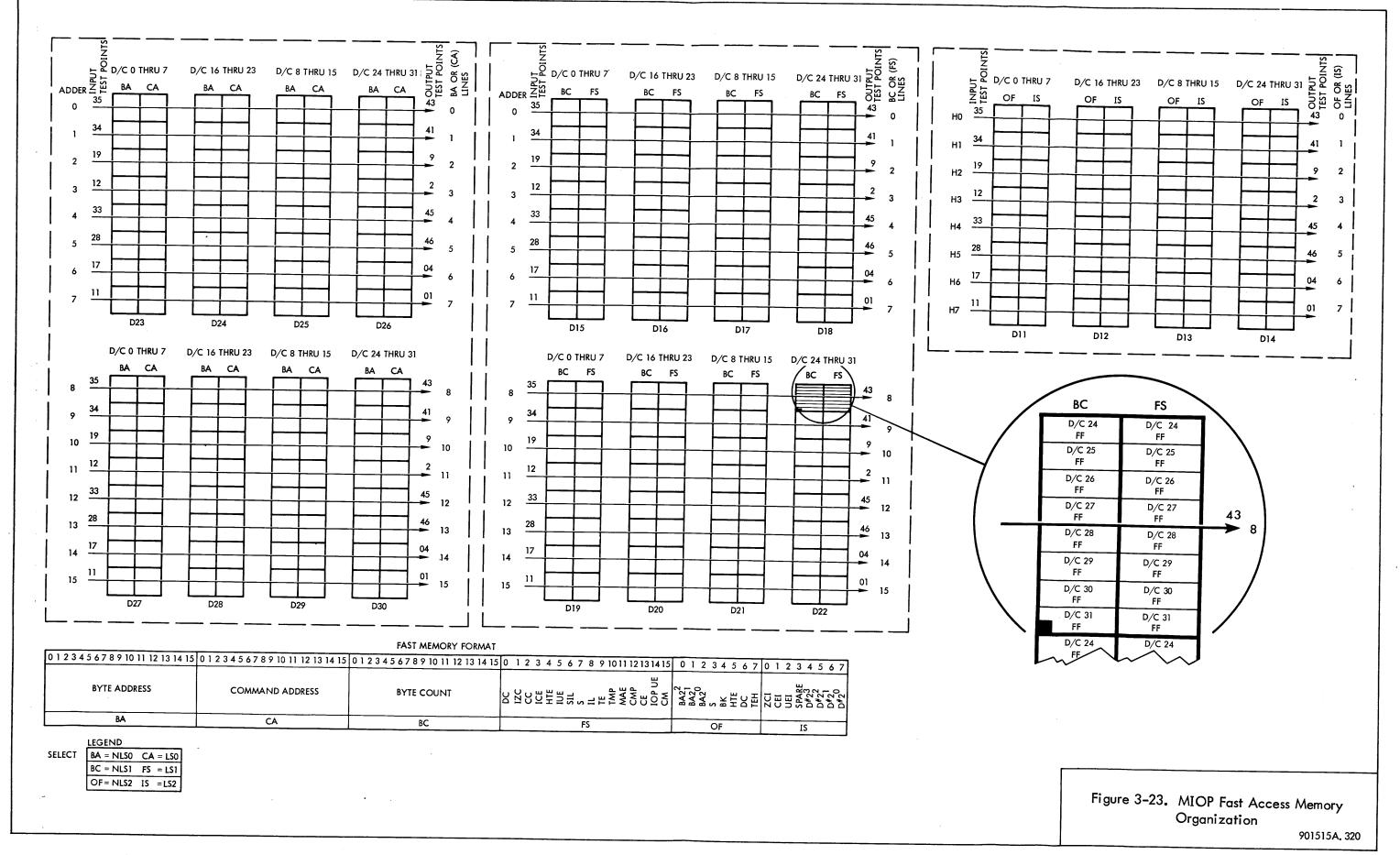

| 3 <b>-2</b> 3 | MIOP Fast Access Memory Organization                                                 | 3-33          |

| 3-24          | Assignment of Subchannel Groups                                                      | 3-35          |

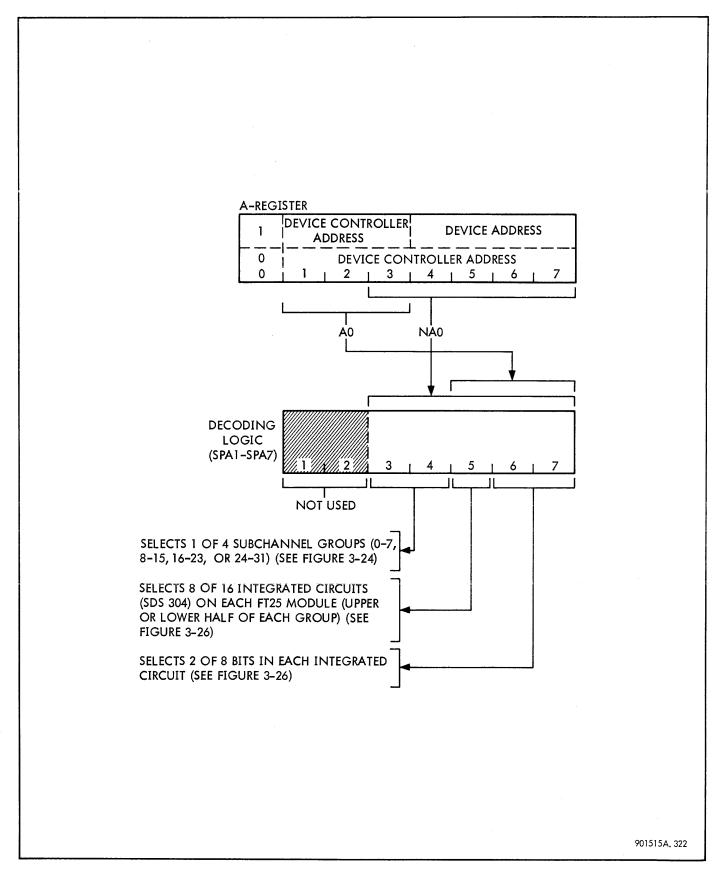

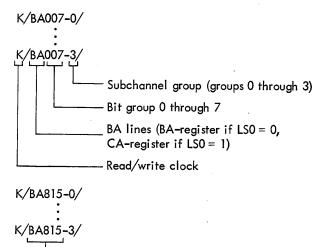

| 3-25          | Decoding the Address Register                                                        | 3-36          |

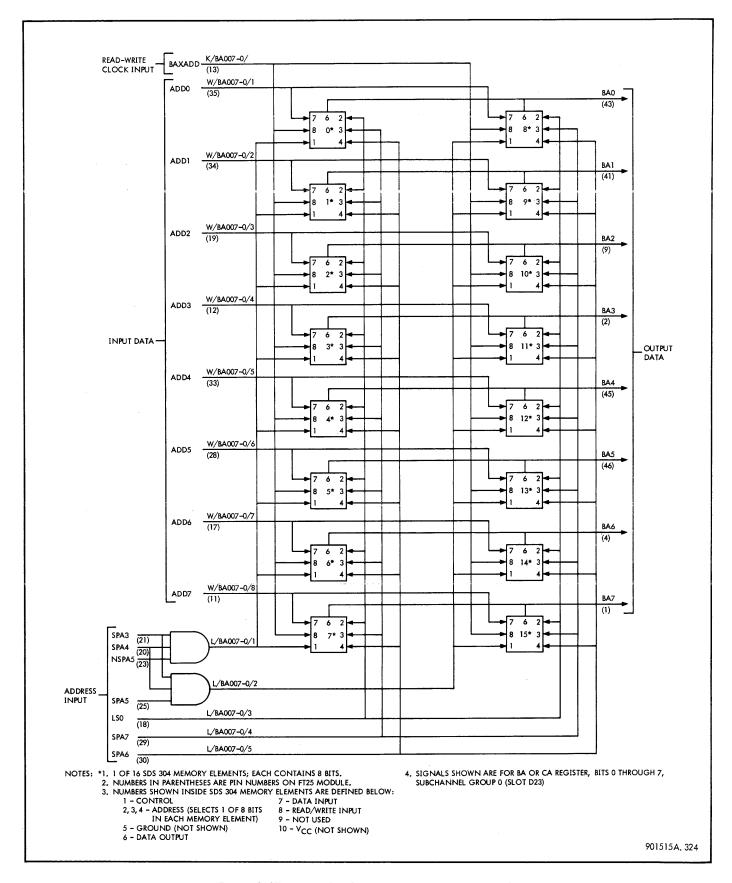

| 3-26          | Decoding SPA5, SPA6, and SPA7 Address Signals to Select One Subchannel in Group Zero | 3-37          |

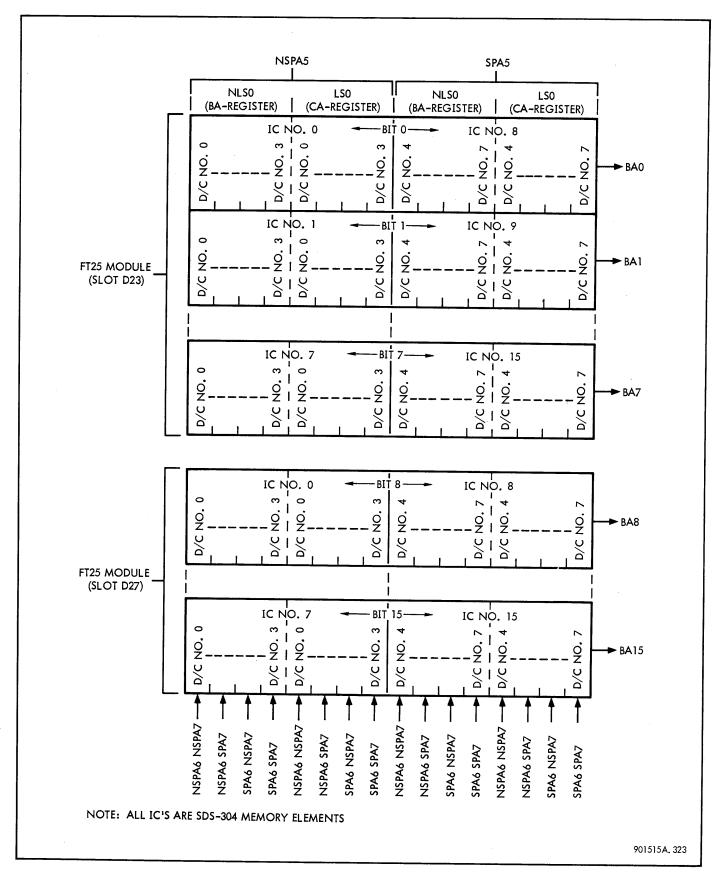

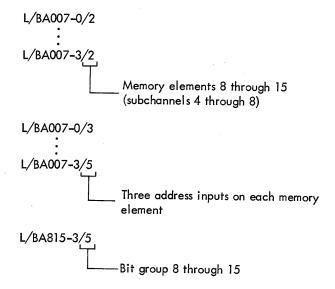

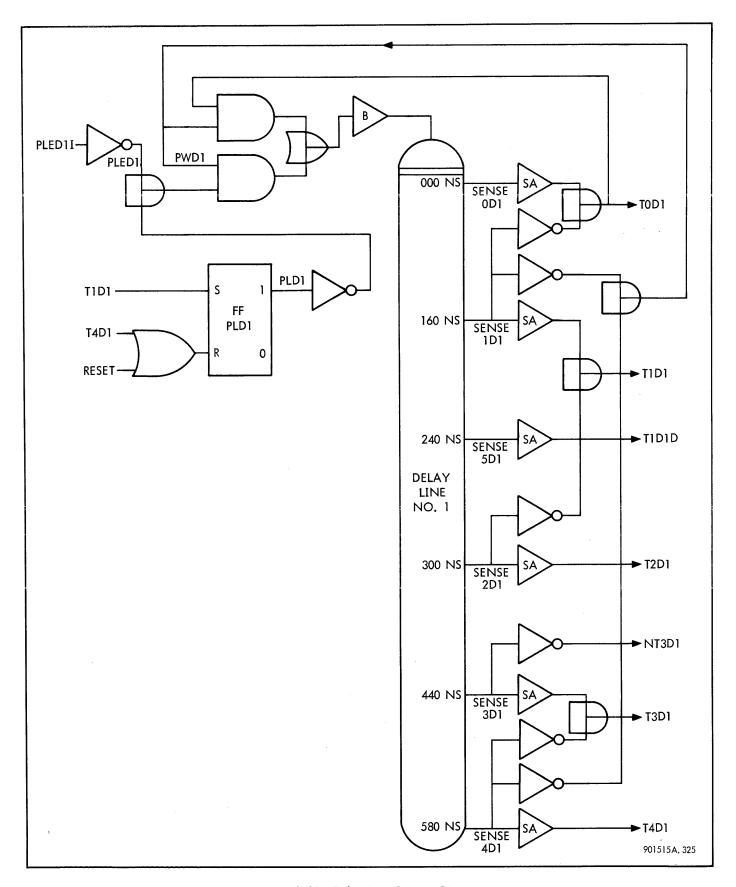

| 3 <b>-2</b> 7 | Typical FT25 Fast Access Memory Module                                               | 3-38          |

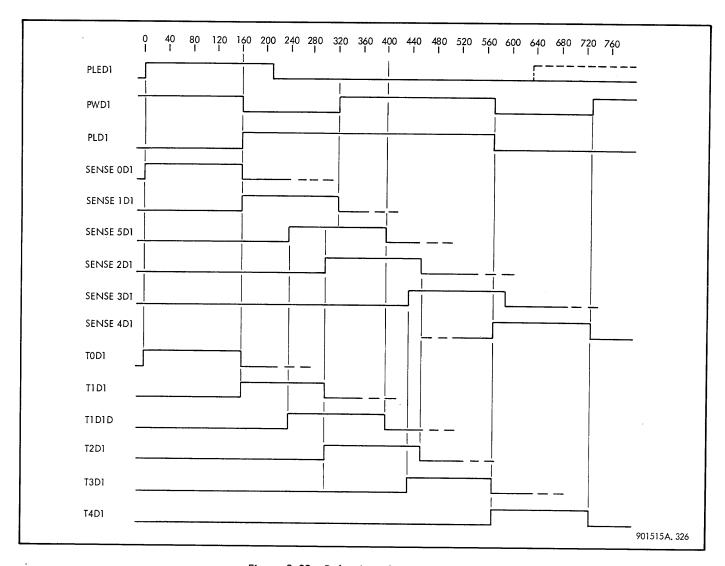

| 3-28          | Delay Line 1 Logic Diagram                                                           | 3-40          |

| 3-29          | Delay Line 1 Timing Signals                                                          | 3-41          |

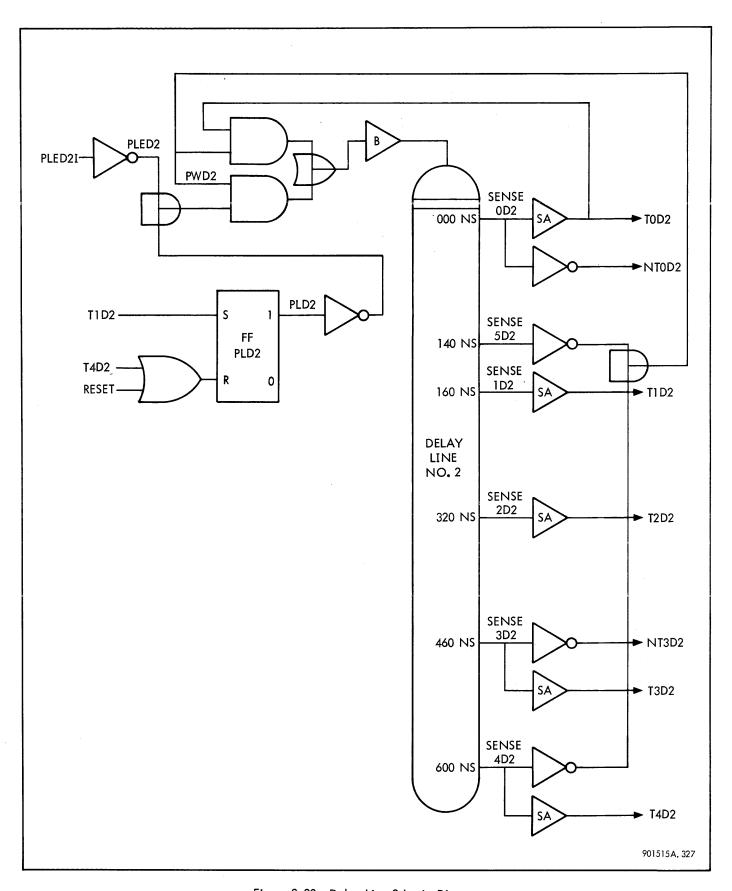

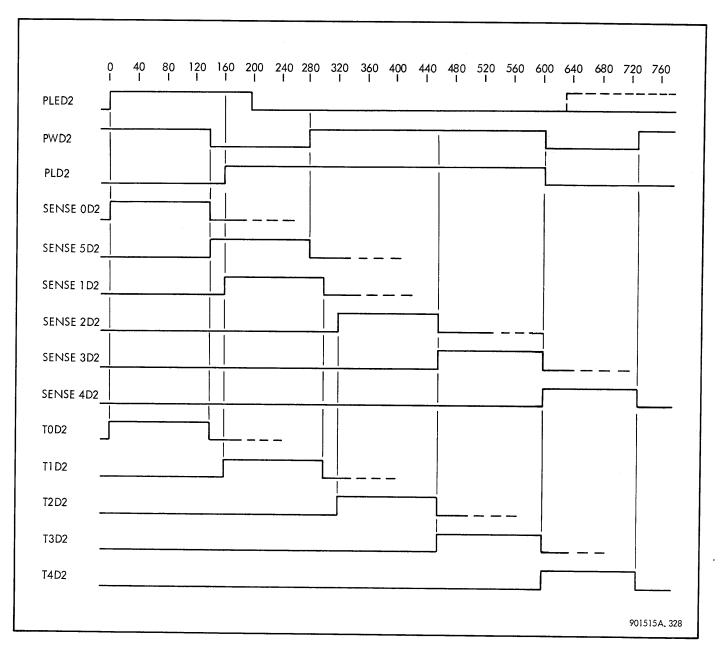

| 3-30          | Delay Line 2 Logic Diagram                                                           | 3-42          |

| 3-31          | Delay Line 2 Timing Diagram                                                          | 3-43          |

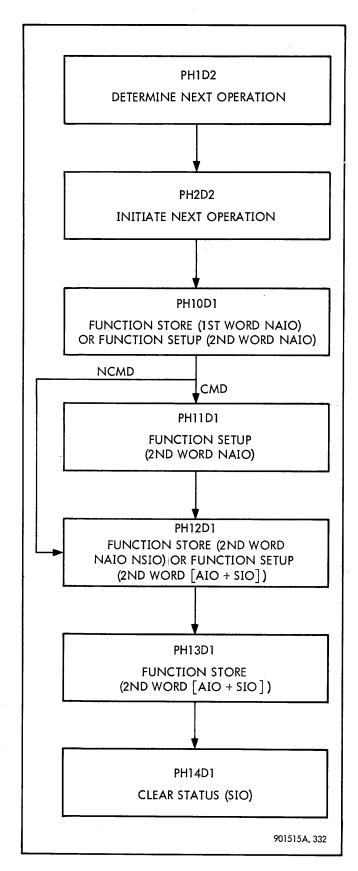

| 3-32          | Phase Diagram for SIO, HIO, TIO, and TDV Instructions                                | 3-45          |

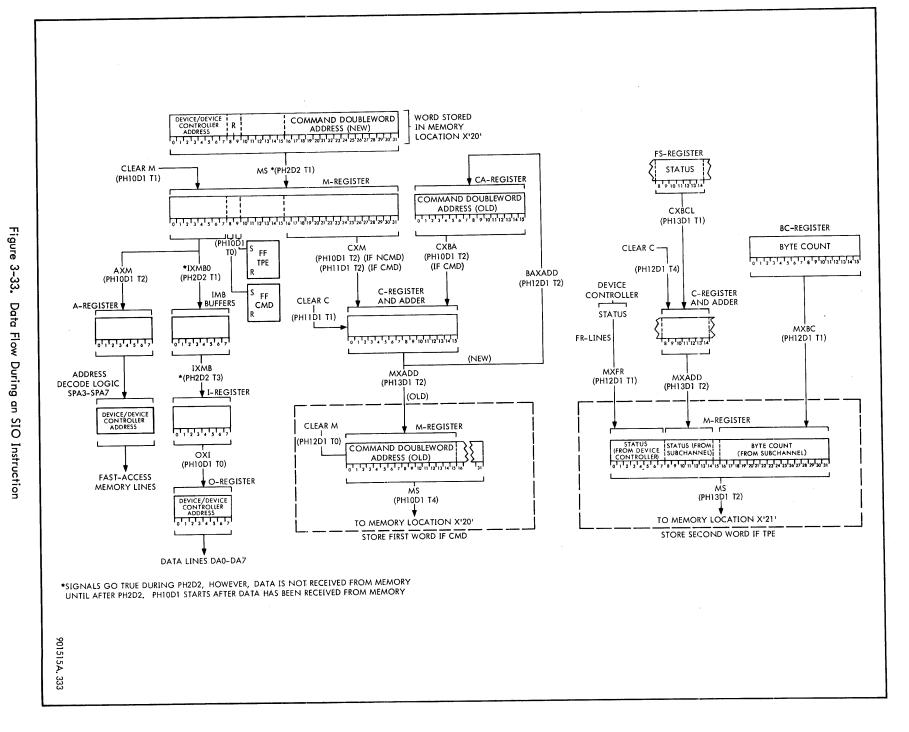

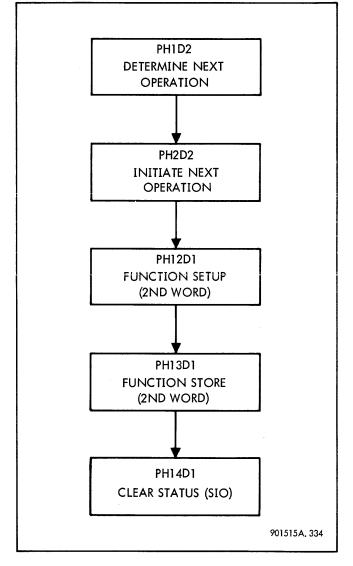

| 3-33          | Data Flow During an SIO Instruction                                                  | 3-46          |

| 3-34          | Phase Diagram for an AIO Instruction                                                 | 3-62          |

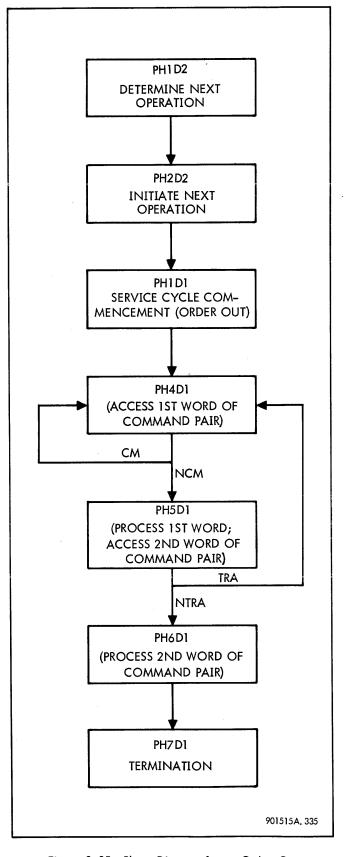

| 3-35          | Phase Diagram for an Order-Out Service Cycle                                         | 3-68          |

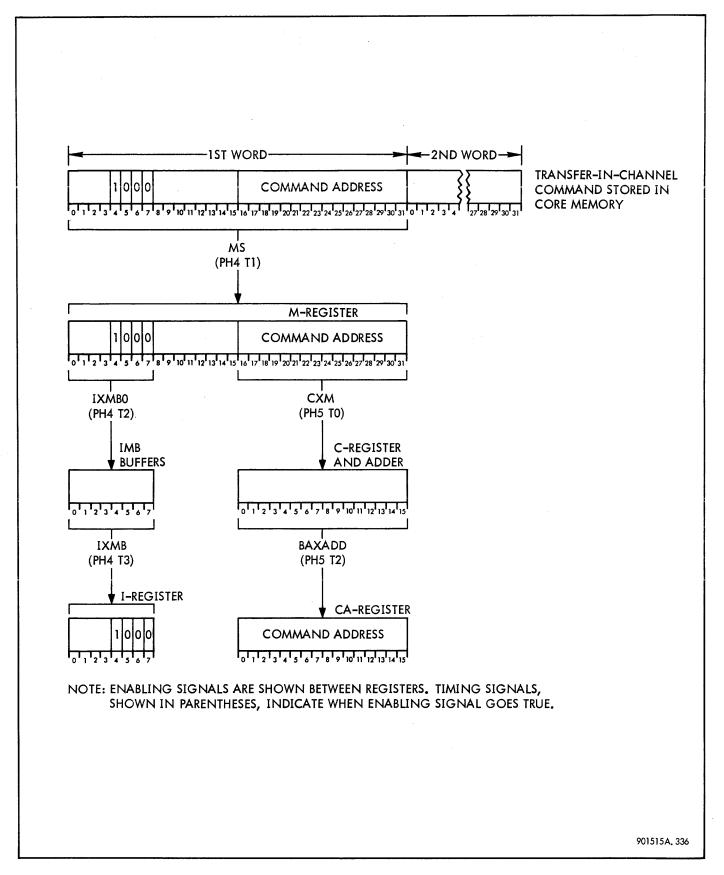

| 3-36          | Processing a Transfer in Channel Command                                             | 3-70          |

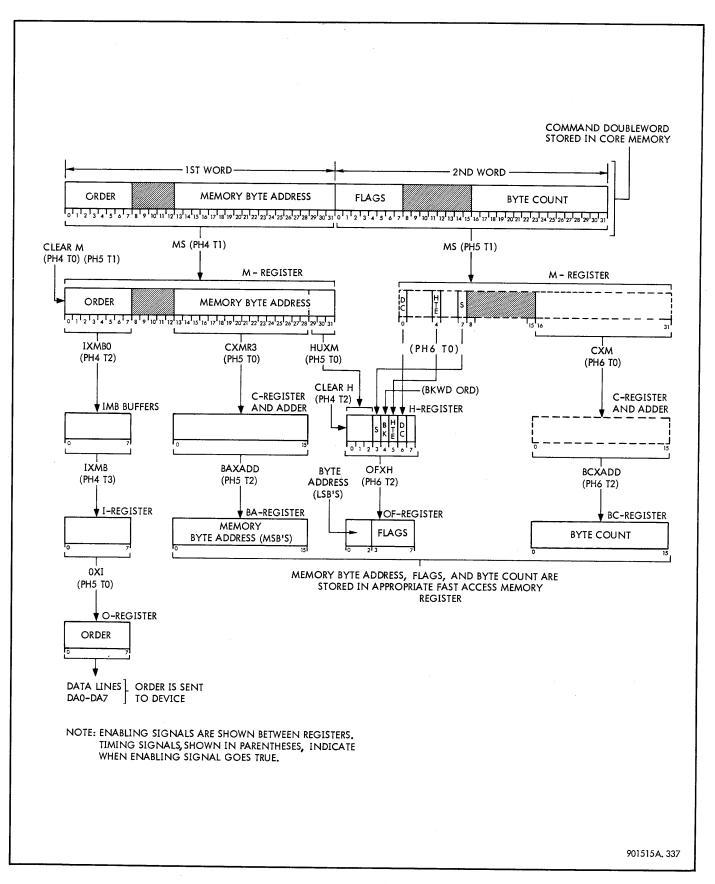

| 3-37          | Processing a Command Doubleword                                                      | 3-71          |

| 3-38          | Termination Phase of an Order-Out Service Cycle                                      | 3-72          |

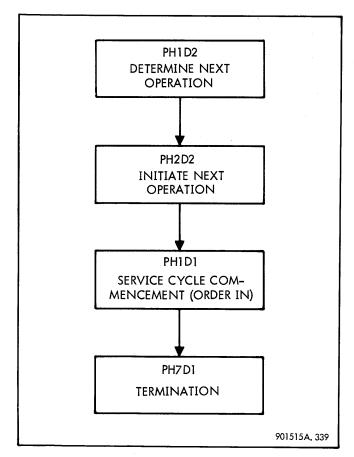

| 3-39          | Phase Sequences For an Order-In Service Cycle                                        | 3 <b>-</b> 85 |

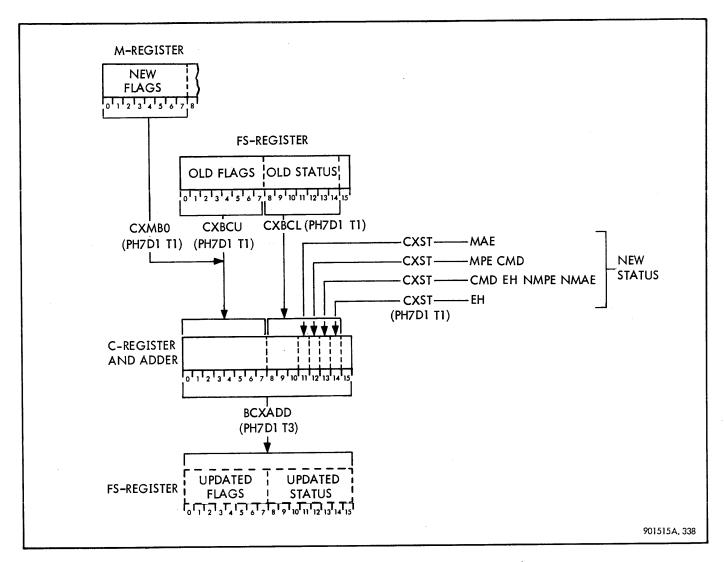

| 3-40          | Updating Flags and Status During an Order-In Service Cycle                           | 3-86          |

| 3-41          | Updating Interrupt Status During an Order-In Service Cycle                           | 3-87          |

| 3-42          | Phase Sequence Diagram For a Data-Out Service Cycle                                  | 3-88          |

| 3-43          | Processing a Data-Out Service Cycle                                                  | 3-96          |

| 3-44          | Processing Data During a Data-Out Service Cycle, Timing Diagram                      | 3-117         |

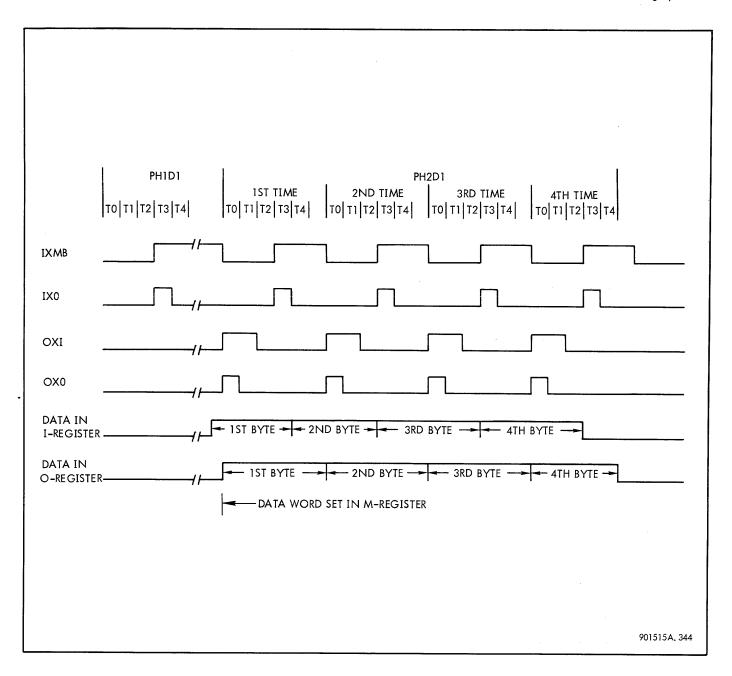

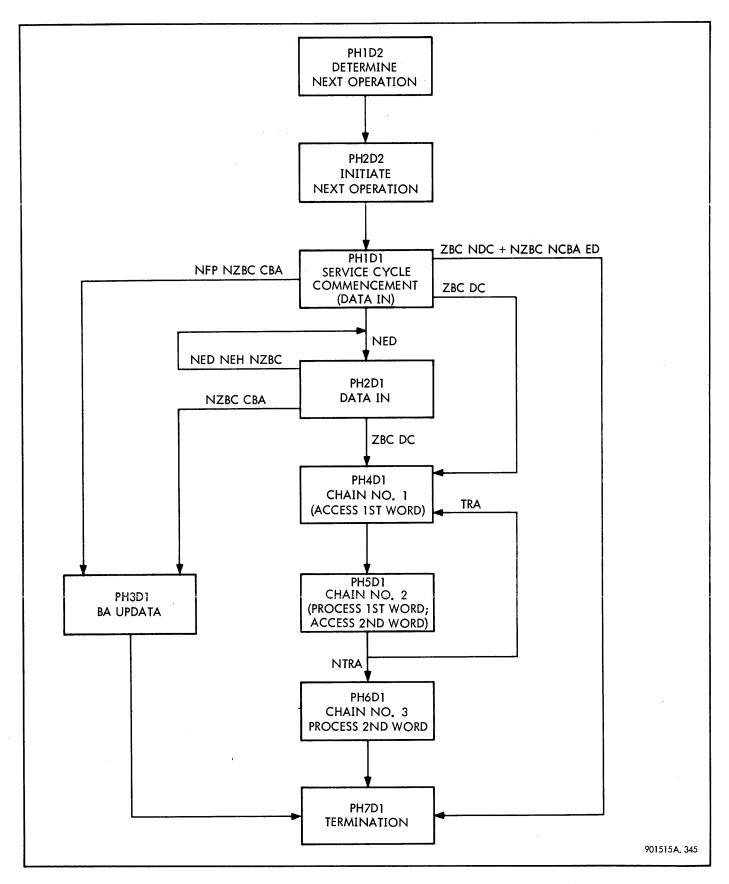

| 3-45          | Phase Sequence Diagram For a Data-In Service Cycle                                   | 3-118         |

| 3-46          | Processing Data During a Data-In Service Cycle                                       | 3-120         |

| 4-1           | MIOP Module Location Chart                                                           | 4-2           |

### RELATED PUBLICATIONS

| Publication Title                                         | Publication No. |

|-----------------------------------------------------------|-----------------|

| SDS Sigma 5 Computer,<br>Reference Manual                 | 900959          |

| SDS Sigma 7 Computer,<br>Reference Manual                 | 900950          |

| SDS Sigma Computer Systems<br>Interface Design Manual     | 900973          |

| SDS Sigma 7 Computer, Technical Manual                    | 901060          |

| SDS Sigma 5 Computer, Technical Manual                    | 901172          |

| SDS Sigma 5 and 7 Systems Test Monitor                    | 901076          |

| SDS Sigma 5 and 7 Buffered Line Printer<br>System Test    | 901085          |

| SDS Sigma 5 and 7 Keyboard-Printer<br>System Test         | 901086          |

| SDS Sigma 5 and 7 Medium–Speed RAD<br>File System Test    | 901090          |

| SDS Sigma 5 and 7 9–Channel Magnetic<br>Tape System Test  | 901110          |

| SDS Sigma 5 and 7 Card Punch System Test                  | 901120          |

| SDS Sigma 5 and 7 Card Reader System Test                 | 901121          |

| SDS Sigma 5 and 7 Paper Tape Reader/<br>Punch System Test | 901122          |

| SDS Sigma 7 Multiplexing IOP Test                         | 901126          |

#### SECTION I GENERAL DESCRIPTION

#### 1-1 INTRODUCTION

This manual describes SDS Multiplexing Input/Output Processor (MIOP) Models 8471 and 8271 and optional subchannels, Models 8472 and 8272. The manual consists of four sections that provide general information, programming information, a functional description, maintenance information, and parts lists.

The MIOP provides independent control of data transfers between core memory and certain peripheral devices, and starts, tests, and acknowledges interrupts pertaining to certain peripherals under control of a Sigma 5 or 7 central processing unit.

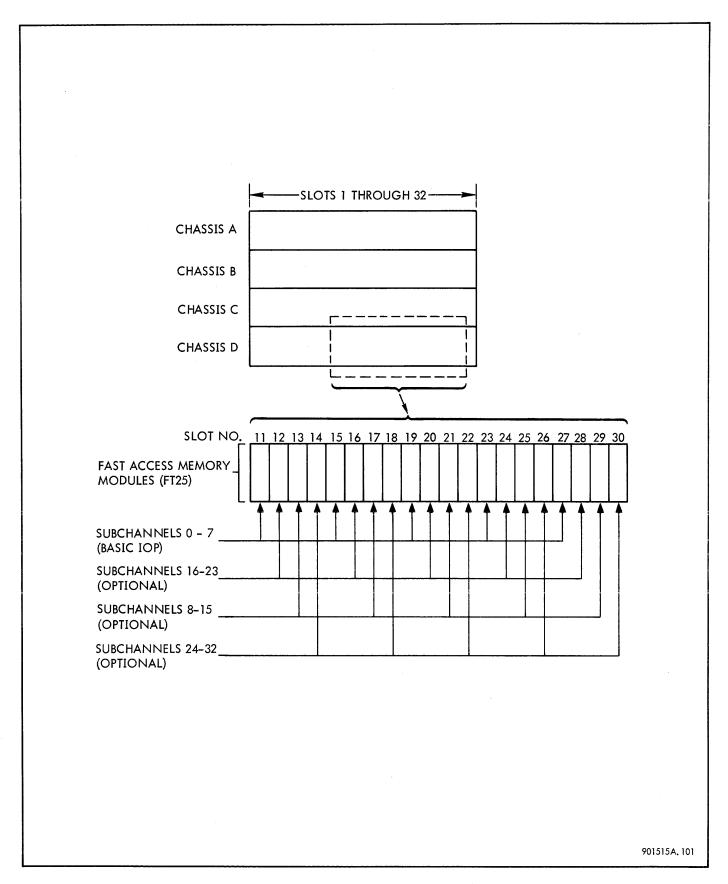

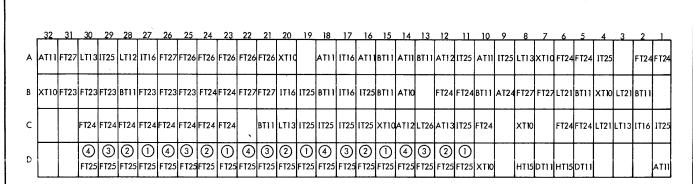

Figure 1–1 shows the physical layout of the basic MIOP, Models 8471 (Sigma 7) and 8271 (Sigma 5), and the optional subchannels, Models 8472 (Sigma 7) and 8272 (Sigma 5).

Technical manuals describing equipment associated with the MIOP are referred to in the list of Related Publications in the front matter of this manual.

#### 1-2 PHYSICAL DESCRIPTION

The basic MIOP consists of 98 modules installed in chassis A, B, C, and D, and includes eight subchannels. Each subchannel accommodates one device controller. Five fast-access memory modules (FT25) provide eight subchannels. Since one fifth of each subchannel is contained on each of the five FT25's, the FT25's must be installed in groups of five. Three additional groups of FT25's provide a total of 32 subchannels.

#### 1-3 FUNCTIONAL DESCRIPTION

The MIOP contains input and output data storage registers and buffers, fast-access memory registers for command manipulation, a timing signal generator, and control logic. The function of the MIOP is to control and sequence input and output operations for a number of peripheral devices simultaneously, allowing the CPU to concentrate on program execution. The active devices time-share the hardware in

the MIOP. Any input-output events that require CPU intervention are brought to the attention of the CPU by means of the interrupt system. The device controllers and devices are described in other manuals.

#### 1-4 SPECIFICATIONS AND LEADING PARTICULARS

The general specifications for the MIOP are given in table 1-1.

Table 1-1. General Specifications

| Power requirements (supplied by PT16 power supply) | +8Vdc (9.0 amps)                                     |

|----------------------------------------------------|------------------------------------------------------|

| by 1110 power suppry)                              | -8Vdc (2, 4 amps)                                    |

|                                                    | +4Vdc (20 amps)                                      |

|                                                    | Total watts: 171                                     |

| Logic signal levels                                | One, +4Vdc; Zero,<br>0v (low impedance<br>to ground) |

| Data format                                        | 8-bit byte, 32-bit<br>word                           |

| Temperature                                        |                                                      |

| Nonoperating:                                      | -40°C to 60°C<br>(-40°F to 140°F)                    |

| Operating:                                         | 5°C to 50°C<br>(41°F to 122°F)                       |

| Relative humidity (operating)                      | 10% to 95%                                           |

| Altitude                                           |                                                      |

| Nonoperating:                                      | 20,000 feet maximum                                  |

| Operating:                                         | 10,000 feet maximum                                  |

|                                                    |                                                      |

Figure 1-1. MIOP Basic and Optional Subchannel Locations

# SECTION II OPERATION AND PROGRAMMING

#### 2-1 GENERAL

The MIOP contains no controls or indicators other than address switches and switch LASTONE, which is closed on all MIOPs connected to a CPU except the last one. These switches are contained on the switch comparator module (LT26) in slot 13 of chassis C. The module contains eight switches; the three address switches that apply to the MIOP are \$1-1, \$2-1, and \$3-1, and the switch that applies to signal LASTONE is \$1-2.

In the Sigma 5 and 7 I/O system, the CPU executes instructions, the MIOP executes commands, and the I/O device executes orders. For example, the CPU may execute a start input/output (SIO) instruction to initiate an I/O

operation. During the course of the operation, the MIOP fetches a command doubleword (command) from the command list in core memory and stores it (except the order bits) in its own fast access memory. The command provides the MIOP with information needed to perform its functions; commands are, therefore, executed by the MIOP. The order bits of the command are transmitted to the device. The order defines the operation to be performed by the device; the I/O devices, therefore, execute orders.

For a description of I/O instructions, commands, and orders, see SDS Sigma 7 Computer Reference Manual 900950 and SDS Sigma 5 Computer Reference Manual 900959.

# SECTION III PRINCIPLES OF OPERATION

#### 3-1 INTRODUCTION

This section describes the principles of operation of the MIOP on a general information level and on a detailed level in terms of the logic equations. The detailed description includes a description of each IOP register, a typical I/O operation, the interface signals, timing generation, interface signals, IOP phase sequences, and a glossary of logic signals. There is a phase sequence description for each CPU-initiated I/O instruction and for each of the four service cycles. Each phase sequence description includes a table that lists every logic operation that occurs in the MIOP relating to the specific instruction or service cycle, starting with the first timing signal of the first phase.

#### 3-2 GENERAL PRINCIPLES OF OPERATION

#### 3-3 GENERAL

The maximum number of devices that can be uniquely addressed by a computer with one MIOP installed is 152. Up to eight MIOP's can be connected to one computer. The basic MIOP is mechanized with eight subchannels that accommodate eight device controllers. Because of the addressing structure of the I/O instructions, only these first eight subchannels can be used for servicing multiunit device controllers. The multiunit device controllers are capable of controlling up to 16 devices each. When the multiunit device controllers are used, the subchannel is shared by all the devices controlled by that device controller. Each subchannel contains all the information necessary to control any I/O operation between core memory and the device.

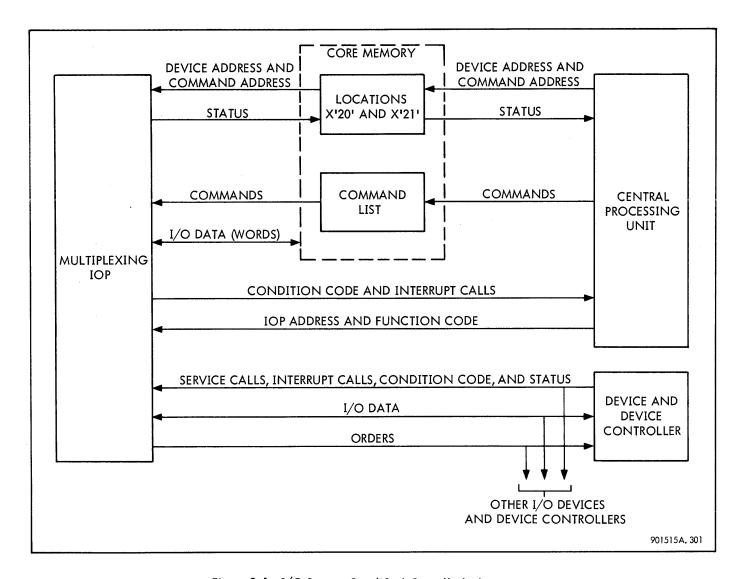

Once an I/O operation has been started by the CPU, the operation is performed to completion by the MIOP, device controller, and core memory without intervention by the CPU. Timing between these units is asynchronous. The MIOP processes the I/O operation while the CPU is performing functions possibly unrelated to the I/O operation. The MIOP controls the I/O operations by executing a command list prepared by the CPU and stored in core memory (figure 3-1).

#### 3-4 OVERALL OPERATION

An I/O operation starts when the CPU issues a start input/output (SIO) instruction addressed to a particular MIOP and device controller. The addressed MIOP, after receiving the address information, places the device controller address on the MIOP/device controller interface lines and waits for a response. The addressed device controller responds by sending condition code and status information to the MIOP.

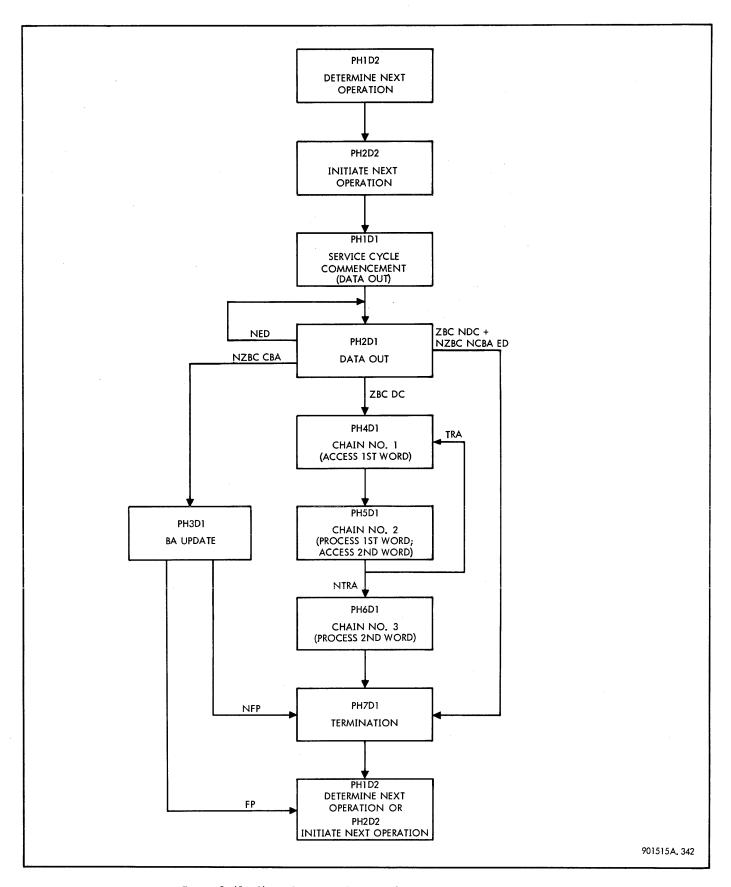

The MIOP sends the condition code information to the CPU and, depending upon the coding of the SIO instruction, may or may not send status and other information related to the MIOP, device, and device controller to the CPU. The SIO instruction, if successful, causes the addressed device controller to make service requests from the MIOP. As a result of the service requests (after the SIO instruction has been concluded), the device controller electrically connects itself to the MIOP/device controller interface lines. The time the device controller is electrically connected is called a service cycle. It is during the service cycles that follow an SIO instruction that data is exchanged between the device controller and core memory. During these service cycles the MIOP performs core memory accesses as required by the device, continually updates information such as byte address and byte count, and controls the I/O operation until it is completed, aborted, or halted by a halt input/output (HIO) instruction.

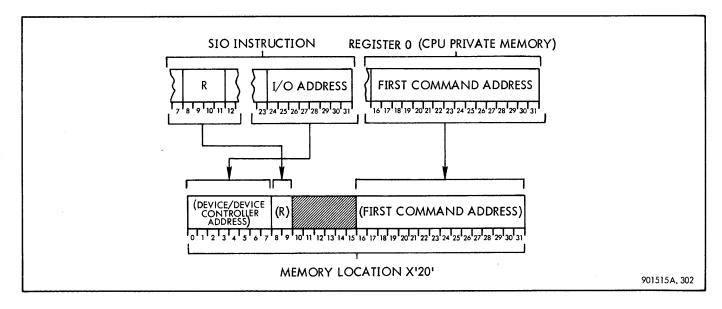

During execution of the I/O instructions, core memory locations, X'20' and X'21' (hexadecimal 20 and 21), are used to exchange information between the MIOP and CPU. These are in addition to the MIOP/CPU interface lines. During the early phases (CPU phases) of an SIO instruction, the CPU writes the address of the device/device controller, the address of the first command doubleword, and the nature of the R field into core memory location X'20' (see figure 3-2).

The function code (SIO) and MIOP address are sent directly to the MIOP on the MIOP/CPU interface lines. The addressed MIOP then reads core memory location X'20', stores the address of the command doubleword in its internal registers, and places the device controller address on the MIOP/DC interface lines. After the addressed device controller responds by sending status and condition code information to the MIOP, the MIOP loads the status and other information (if the CPU so specifies by the coding of the R field of the instruction) into core memory location X'20' and X'21', where it is available to the CPU. The other information consists of information previously stored in the subchannel for the addressed device controller. The condition code is sent directly to the CPU.

At the conclusion of a successful SIO instruction, the device controller starts making service requests to the MIOP. The first service request, which will be for an order out, causes the MIOP to access the command list in core memory for the first command doubleword. The address of the command doubleword was obtained from the CPU during the SIO instruction. The order that is encoded in the command doubleword is sent to the device controller so that it will know what

Figure 3-1. I/O System, Simplified Overall Block Diagram

Figure 3-2. Loading Core Memory Location X'20' During an SIO Instruction

function to perform. The balance of the command double-word is related to the I/O operation and is retained by the MIOP. This information directs the operations of the MIOP until the I/O operation is concluded. The exchange of I/O data takes place after the device controller has received the order.

As a result of subsequent service requests from the device controller, data is exchanged between core memory and the device through the MIOP. The exchange of data between core memory and the MIOP is on a word basis and between the IOP and the device controller on a byte basis. A maximum of four bytes of data may be exchanged between the MIOP and device controller for each service request. For example, if the order the device received initially was a write order, the operation would be an output operation. In this case, as a result of a service request from the device controller, the MIOP would access core memory for one word of data and store it in an MIOP register. The word is then fed to the device controller one byte at a time. If the order the device received was a read order, the operation would be an input operation. During an input operation, the MIOP accepts data from the device controller one byte at a time and stores it until it has a maximum of four bytes. The four bytes (one word) are then stored in core memory by the MIOP. In addition to transferring I/O data, the MIOP keeps track of the number of bytes of data transmitted and their core memory locations, records status for future interrogations by the CPU, checks parity, and performs other operations as required.

#### 3-5 Interrupt Calls

Interrupt calls made by a device controller are passed along to the CPU by the MIOP. One standard interrupt level is provided to service all interrupts generated by all devices connected to all MIOP's controlled by a CPU. In response to an interrupt call, the CPU issues an acknowledge input/ output interrupt (AIO) instruction. The primary purpose of the AIO is to determine the address of the interrupting IOP and device controller. The highest priority device controller with an interrupt pending sends its address (along with status and condition code information) to the MIOP. The MIOP writes its own address, the device controller address, and status information in memory location X'20' and sends the condition code information to the CPU. The CPU then reads memory location X'20' to acquire the address and status, and takes action based on the status and condition code information it has just received.

#### 3-6 Chaining

Chaining is the term applied to the operation that permits an activity to continue after the functions specified by the current command have been completed. The MIOP employs both data chaining and command chaining. Both types of chaining are controlled by a flag setting of the current command and result in a new command being fetched by the MIOP when all data specified by the current command has been transferred. Each new command fetched by the MIOP is the next command in sequence in the command list in core memory.

Data chaining is used for scatter-read or gather-write operations, where the peripheral device is operating with a record of continuous data that may come from, or be delivered to, noncontiguous areas of core memory in subblocks of any size specified by the programmer.

Command chaining provides a means of writing a program to operate on several records without intervention by the CPU. Command chaining causes the MIOP to load a new command at the end of a record, send the new order to the device controller, and start processing the new record.

#### 3-7 DETAILED PRINCIPLES OF OPERATION

#### 3-8 MIOP REGISTERS

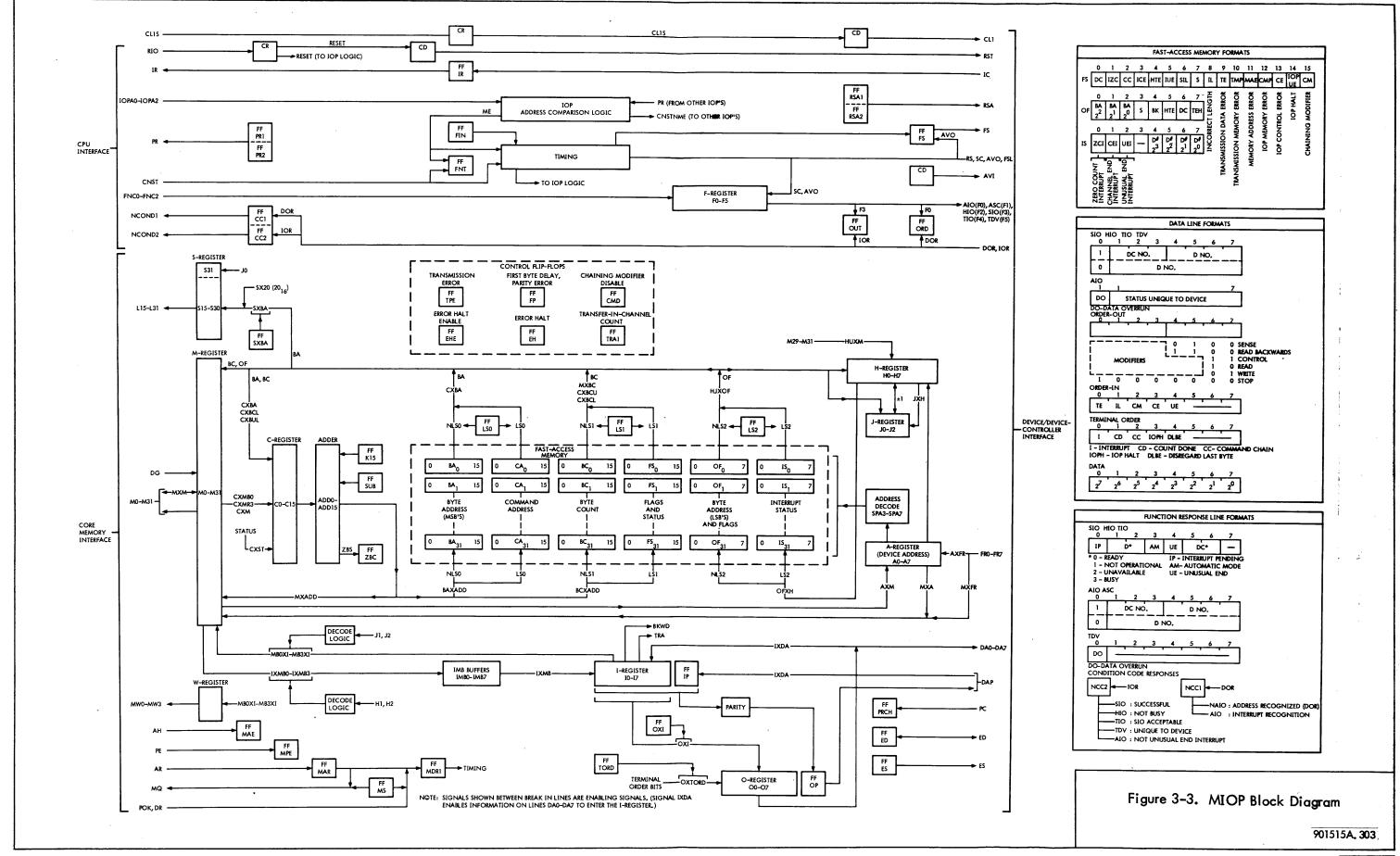

The various data and control registers within the MIOP are shown in figure 3-3. The MIOP address logic and timing is shown as a single block, since these two sections are described separately. For convenience, the formats of the subchannel registers, the data lines, and the function response lines are also included in figure 3-3. With the description of each register is a flow diagram showing the source of all input signals to that register. The transfer signal that enables the input signals to enter the registers is shown in the break of the line connecting the input source to the register.

#### 3-9 A-Register

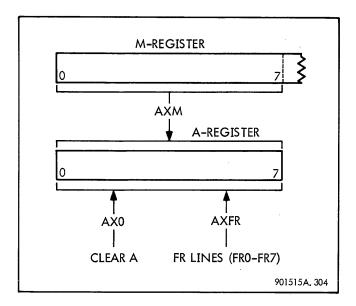

The A-register (see figure 3-4) consists of eight buffer latches, A0 through A7, and normally contains the device/device controller address. During execution of an instruction (except an AIO), the A-register receives the address information from the M-register. During an acknowledge service call (ASC) function and an AIO instruction, the A-register receives the address from a device controller by means of the FR lines. The address in the A-register is decoded by the address decoding logic (SPA3 through SPA7) to select one of the 32 possible subchannels (see figure 3-25). The A-register is cleared to zeros when signal AXO is true.

#### 3-10 C-Register

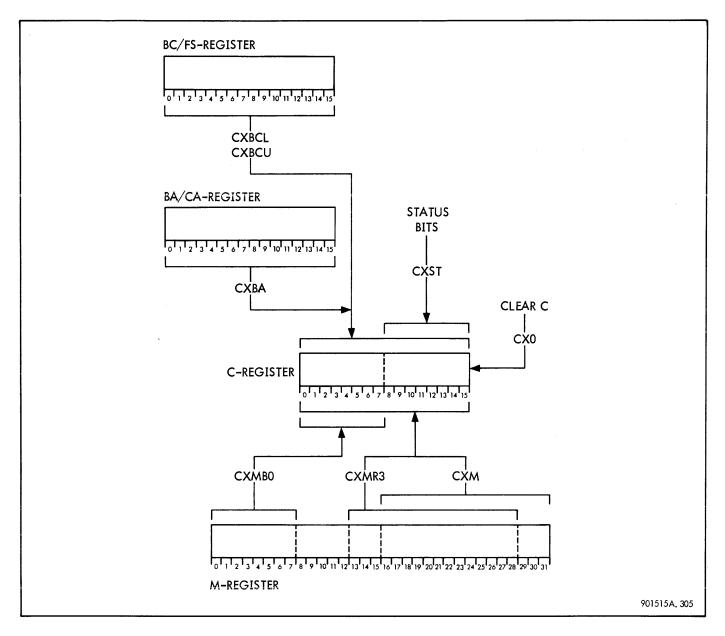

The C-register (see figure 3-5) consists of 15 buffer latches. CO through C14, and one buffered latch, flip-flop C15. The C-register is the only input to the adder. The C-register, with the adder, is used as a common point for the distribution of data between various MIOP registers. The C-register is also used with the adder and two buffered latches (K15 and SUB), as a means of incrementing or decrementing a number by one. Input data to the C-register consists of status information which comes from various sources, the Mregister, the BA lines, and the BC lines. When signal LSO is true, the information on the BA lines is the output of the command address (CA) register, and when signal LSO is false, the information on the BA lines is the output of the byte address (BA) register. When signal LS1 is true, the information on the BC lines is the output of the flags and status (FS) register, and when signal LS1 is false, the information on the BC lines is the output of the byte count (BC) register. The C-register is cleared to zeros when signal CX0 is true.

Figure 3-4. A-Register Inputs

#### 3-11 CA-Register

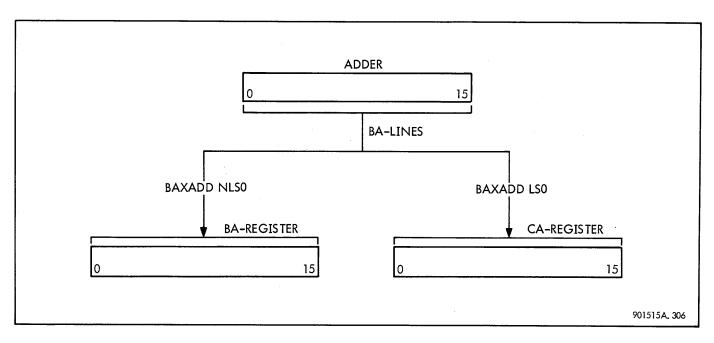

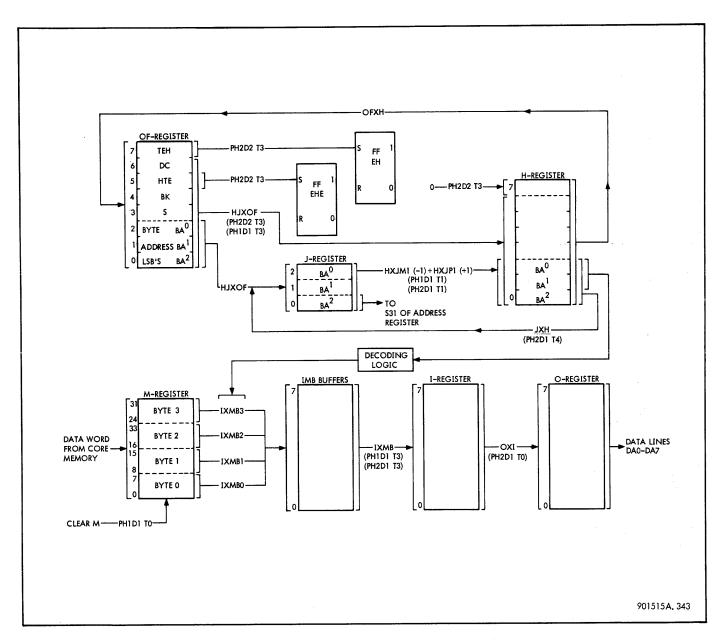

The CA-register (see figure 3-6) is one of the six registers that comprise each of the 32 possible subchannels. Each CA-register consists of 16 fast-access flip-flops, CA0 through CA15. This register holds the current command doubleword plus one. During execution of an instruction (when the current command doubleword is to be sent back to the CPU as part of the response information), the contents of the CA-register are transferred through the adder and decremented by one. During chaining operations, the contents of the CA-register are circulated through the Cregister and adder to increment them by one every time a command doubleword is accessed from core memory. The CA-register receives its input data from the adder. The output of the CA-register is available to the C-, M-, and S-registers. Both the input data lines and the output data lines of the CA-register are shared with the BA-register.

The command address (16 bits) is set into the 16 most significant bits (MSB) of the S-register whenever a new command doubleword is to be accessed. The 17th bit, S31, which is the least significant bit (LSB) of the S-register, is controlled separately. This permits the MIOP to access the first word of the command doubleword when S31 is false and to access the second word when it is true.

#### 3-12 BA-Register

The BA-register (see figure 3-6) is one of the six registers that comprise each of the 32 possible subchannels. Each BA-register consists of 16 fast-access flip-flops, BAO through BA15. This register contains the 16 MSB's of the current byte address. The three LSB's of the byte address are contained in the OF-register (see figure 3-46). Bit position OF2 is the LSB of the byte address and OF0 is the third LSB. The 16 bits (BAO through BA15) of the BA-register and OF0 constitute a word address in core memory.

The two LSB's (OF2 and OF1) define the particular byte of that word. Every time a byte of data is processed the byte address is incremented or decremented as required. After every fourth byte a carry to, or borrow from, the LSB of the word address (OF0) is required. The BA-register contents must, therefore, be updated when a carry to, or borrow from, the three LSB's in the OF-register occurs. Whether the byte address is incremented or decremented depends on the backward flag (BK) stored in the OF-register. This flag is true only if a read backward order was sent to the device. When the device is reading backward, data received from that device is written into descending core memory locations. Therefore, the byte address must be decremented by one with each byte processed. If the BK flag is false, the byte address is incremented by one with each byte processed.

#### 3-13 BC-Register

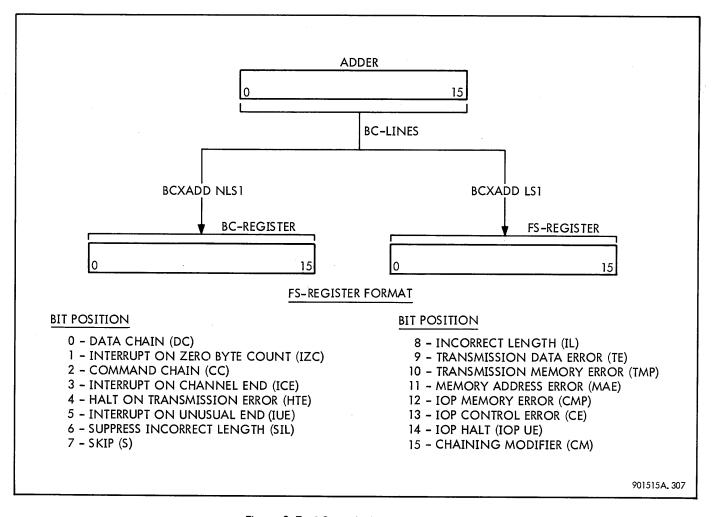

The BC-register (see figure 3-7) is one of the six registers that comprise each of the 32 possible subchannels. Each BC-register consists of 16 fast-access flip-flops, BCO through BC15, and contains the current byte count. During a data-in or data-out operation, the byte count is decremented by one by circulating it through the C-register and adder after each byte of data is processed. The BC-register receives its input data from the adder. The output of the BC-register is available to the C-register when decrementing during a data operation and the M-register as part of the response information during execution of an instruction. Both the input data lines and the output data lines of the BC-register are shared with the FS-register. The BC-register is addressed when signal LS1 is false.

#### 3-14 FS-Register

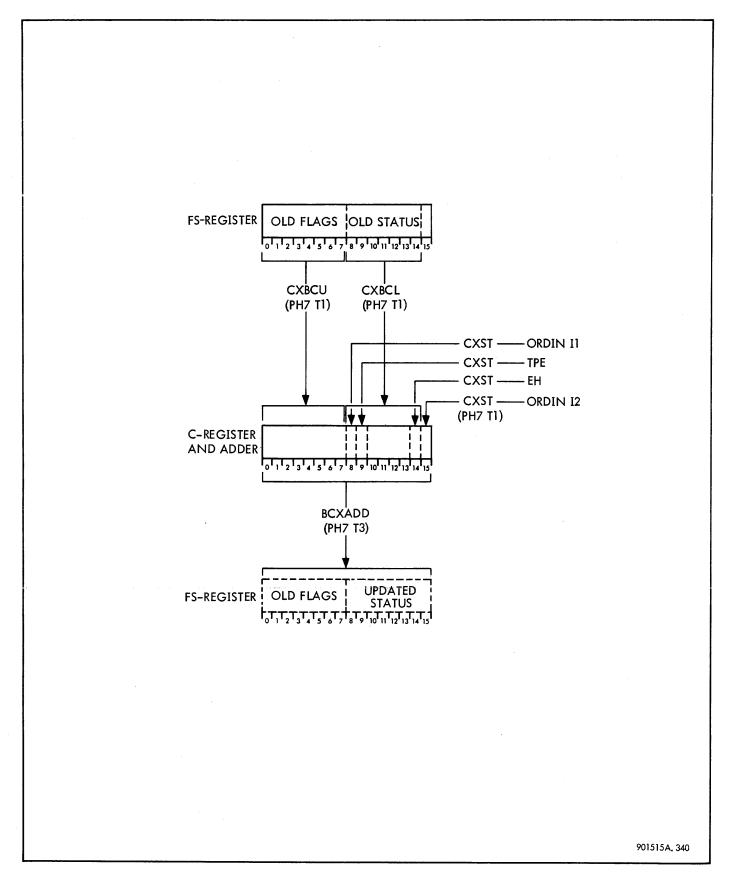

The FS-register (see figure 3-7) is one of the six registers that comprise each of the 32 possible subchannels. Each FS-register consists of 16 fast-access flip-flops, FSO through FS15. The upper half of the FS-register (bits FSO through FS7) contains the flags specified by the command doubleword. During an order-out service cycle, the second word of the command doubleword is set into the M-register. During the termination phase of the service cycle, if there are no error conditions detected, the flags from the command doubleword are transferred from the M-register by means of the C-register and adder to the FS-register (see figure 3-38). If error conditions are detected, the old flags are effectively retained by the FS-register. During an order-in service cycle, the old flags are retained by the FS-register.

The lower half of the FS-register (bits FS8 through FS15) contains status information. The status information is updated during the service cycles. Figures 3-38 and 3-40 show the source of status update information during an order-out and order-in service cycle. An OR operation is performed on the new status, acquired during the service cycle, with part of the old status in the FS-register. The flags and status control the operations of the MIOP during the service cycles.

Figure 3-5. C-Register Inputs

Both the input data lines and the output data lines of the FS-register are shared with the BC-register. The FS-register is addressed when signal LSI is true.

#### 3-15 OF-Register

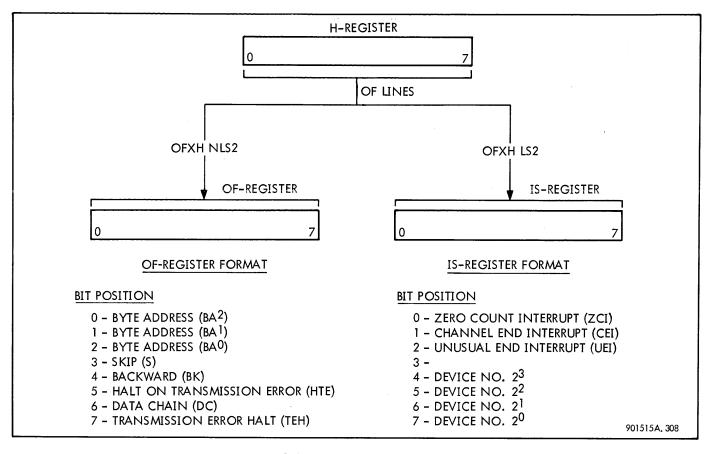

The OF-register (see figure 3-8) is one of six registers that comprise each of the 32 possible subchannels. Each OF-register consists of eight fast-access flip-flops, OF0 through OF7. Bit positions OF0 through OF2 contain the three LSB's of the current byte address. The 16 MSB's of the byte address are contained in the BA-register (see paragraph 3-12). Bit positions OF3 through OF7 contain operating flags. The flags in bits OF3, OF5, and OF6 are duplicates of the flags specified in the command doubleword. Bit OF4 is the backward (BK) flag. This flag is set during an order-out service

cycle if the order bits of the command doubleword specify a read backward order. Figure 3-37 shows how the three LSB's of the byte address (bits OF0 through OF2) and the four flags in bits OF3 through OF6 are set. Bit OF7 contains the transmission error halt (TEH) flag. This flag is set during a data-in service cycle if an error condition is detected too late in that service cycle for the MIOP to report error halt to the device by means of a terminal order. In effect, the error is recorded by the TEH flag until the next communication with that device, at which time the error condition may be used to halt the device.

The OF- and IS-registers share the same input data lines and the same output data lines. The OF-register is addressed when LS2 is false.

Figure 3-6. BA- and CA-Register Inputs

Figure 3-7. BC- and FS-Register Inputs

Figure 3-8. OF- and IS-Register Inputs

#### 3-16 IS-Register

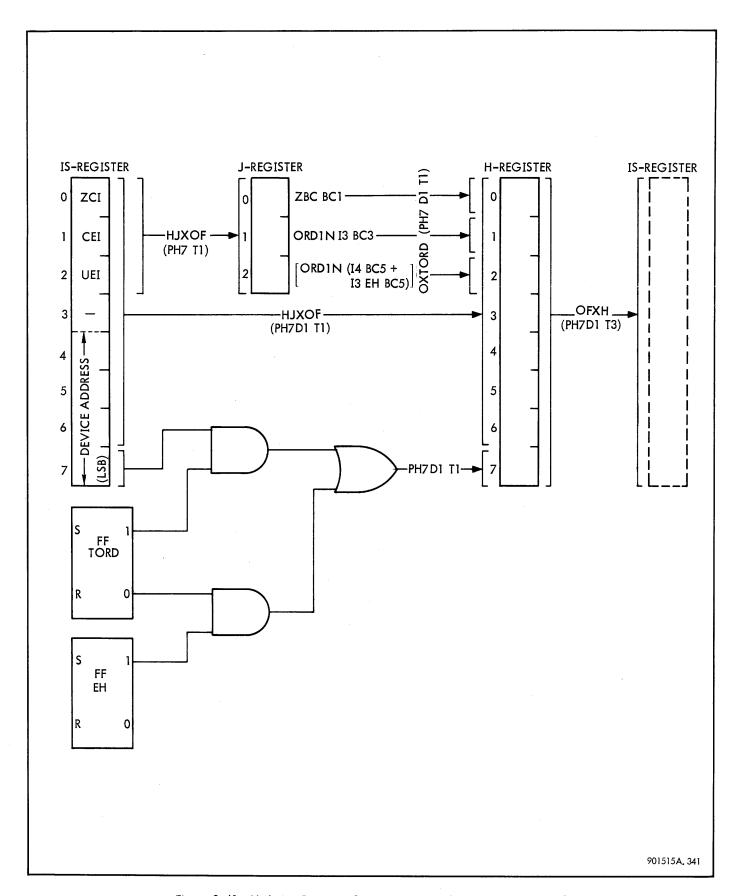

The IS-register (see figure 3-8) is one of six registers that comprise each of the 32 possible subchannels. Each ISregister consists of eight fast-access flip-flops, ISO through IS7. Bits ISO through IS2 contain the interrupt status. These three flags are sent to the CPU as part of the status information during an AIO instruction. The flags are updated as shown in figure 3-41 during an order-in service cycle. Bit IS3 is not used. Bits IS4 through IS7 contain the address of the last successfully started (by means of an SIO) device connected to the device controller associated with this subchannel. This address pertains only to subchannels associated with multiunit device controllers. All devices controlled by a multiunit device controller share the subchannel assigned to that device controller. It is, therefore, possible that the information stored in the subchannel is for a device other than the one requesting an interrupt. During an SIO instruction, the address in the IS-register is compared with the address presently being offered to the MIOP by the interrupting device. If they compare, the information stored in the subchannel is for that device, and can be sent to the CPU.

Both the input data lines and the output data lines are shared by the OF-register. The IS-register is addressed when LS2 is true.

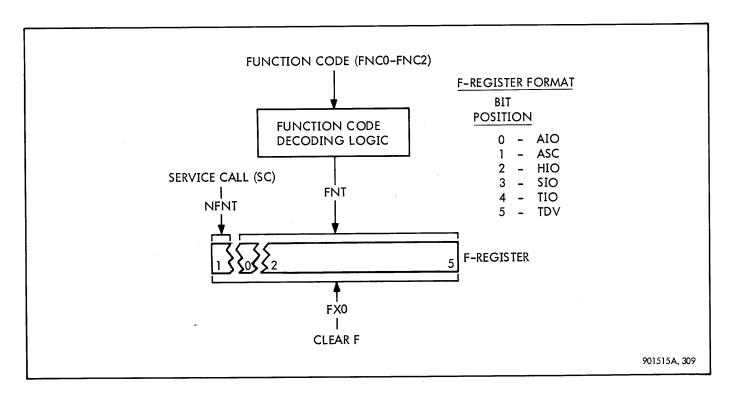

#### 3-17 F-Register

The F-register (see figure 3-9) consists of six buffered latch flip-flops, F0 through F5. Flip-flops F0, and F2 through F5 accept decoded information from the three CPU function code lines, FNC0 through FNC2, and provide on a single function indicator line, the function to be performed (SIO, HIO, TIO, TDV, or AIO). Function indicator line ASC is controlled by F1. Flip-flop F1 is set when one or more device controllers drive the service call (SC) line true. The F-register flip-flops are reset by signal FX0. Signal FNT is true during a CPU-initiated function that is addressed to this MIOP.

The function code lines are decoded by the function code decoding logic as follows:

#### Instruction SIO TIO TDV HIO **AIO** Function Code Line <u>(F0)</u> (F3) (F4) (F5)(F2)FNC0 0 0 0 0 1 0 **FNC1** 0 1 1 1 FNC2 0 1 0 1 0

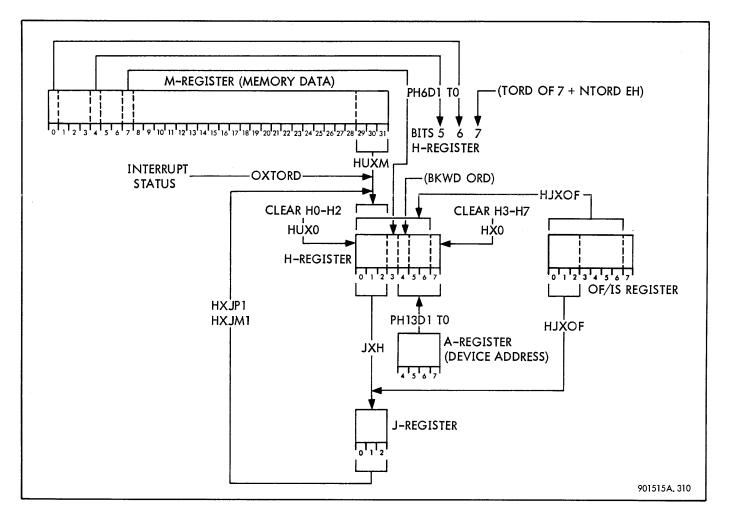

#### 3-18 H-Register

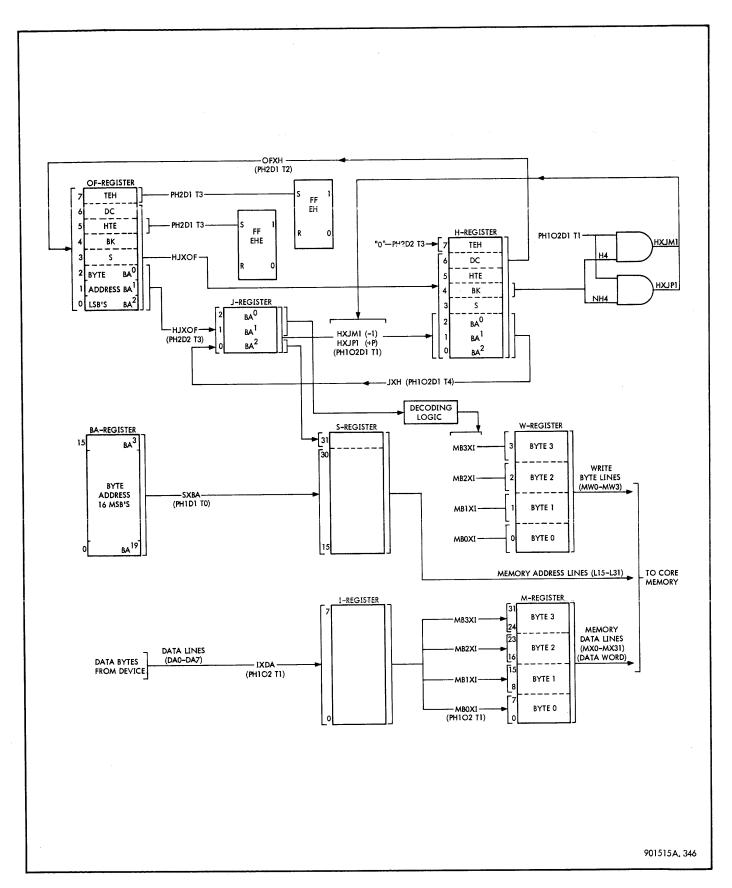

The H-register (see figure 3-10) consists of eight buffered latch flip-flops, H0 through H7. The H-register is used primarily as a temporary storage register for the data in the OF- and IS-registers while the data is operated on. Figure 3-46 shows how the H-register is used with the J-register to increment or decrement the byte address during a data-in service cycle. The H-register is the only input to the OF- and IS-registers.

#### 3-19 J-Register

The J-register (see figure 3-10) consists of three buffered latch flip-flops, J0 through J2. The J-register is used to increment the H-register when signal HXJP1 is true and decrement it when signal HXJM1 is true. Signal HXJM1 is true only when a device is performing a read backward operation. Signal HXJP1 may be true when a device is performing a read (forward) or write operation. The three upper bits of the H-register (H0 through H2) are cleared by signal HUX0, and the five lower bits (H3 through H7) are cleared by signal HX0.

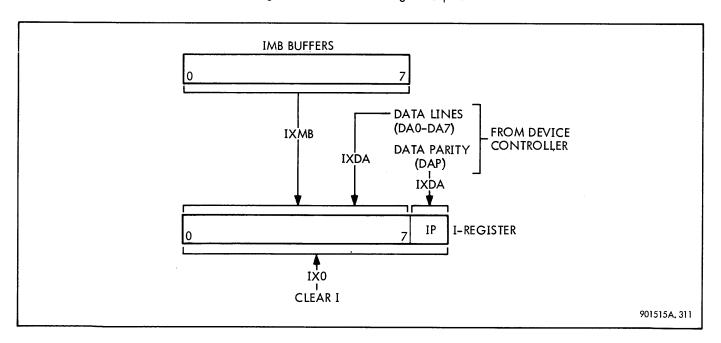

#### 3-20 I-Register

The I-register (see figure 3-11) consists of nine buffer latches, I0 through I7, and IP. The I-register accepts data from the device controller as shown in figure 3-46. Bit IP is also controlled by signal DAP during a data-in service cycle if the device is capable of transmitting a parity bit. If the device is not mechanized to check parity, the device

controller drives the parity check (PC) line true. This causes the MIOP to ignore the parity information supplied by the device controller. During an order-in service cycle, the operational status byte from the device controller is set into bits IO through I7 for subsequent storage in the subchannel registers by means of the H-register, and the C-register and adder. During a data-in service cycle, the input data in the I-register is transmitted to the M-register for subsequent writing into core memory.

During an output operation (data out or order out), the I-register receives the data or order from core memory by means of the M-register and IMB buffers, and sends it to the O-register where it is available to the data lines and thus the device controller. Figure 3-43 shows the processing of output data. The I-register is cleared by signal IXO.

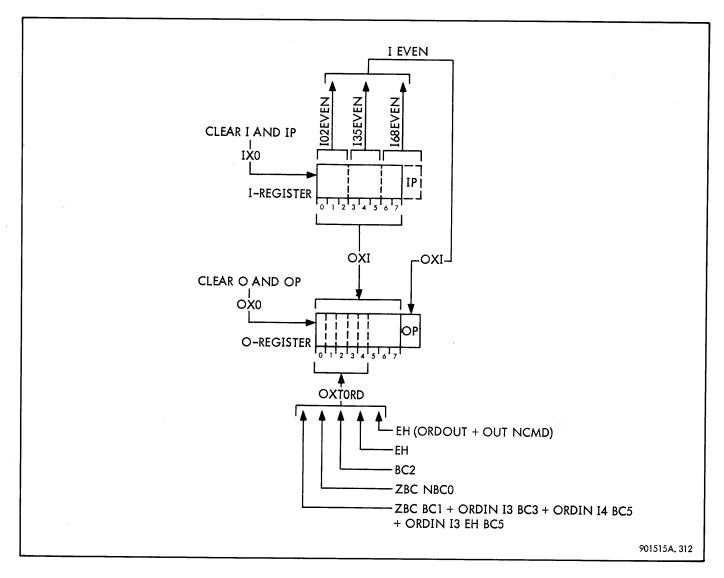

#### 3-21 O-Register